# Digital Logic Design (CS302) Final Term Exam

**Total marks = 80**

Date 17th of Feb 2018

**40 Marks**

## **Objectives**

- 1. The address from which the data is read, is provided by \_

- Depends on circuitry

- None of given options

- ➢ RAM

- Microprocessor

- 2. The best state assignment tends to \_\_\_\_\_

- > Maximizes the number of state variables that don't change in a group of related states

- Minimizes the number of state variables that don't change in a group of related states

- Minimize the equivalent states

- None of given options

#### 3. The total amount of memory that is supported by any digital system depends upon \_\_\_\_\_

- The organization of memory

- The structure of memory

- > The size of decoding unit

- The size of the address bus of the microprocessor

- 4. The expression F=A+B+C describes the operation of three bits \_\_\_\_\_ Gate.

- > OR

- > AND

- > NOT

- > NAND

5. The output of this circuit is always \_\_\_\_\_.

+Vcc Ā 6. A Nibble consists of \_\_\_\_\_ bits 4

- > 8

- ▶ 16

#### 7. In asynchronous transmission when the transmission line is idle, \_\_\_\_\_

- It is set to logic low

- It is set to logic high

- Remains in previous state

- State of transmission line is not used to start transmission

### 8. The \_\_\_\_\_\_ input overrides the \_\_\_\_\_\_ input

- Asynchronous, synchronous

- Synchronous, asynchronous

- Preset input (PRE), Clear input (CLR)

- Clear input (CLR), Preset input (PRE)

9. In a sequential circuit the next state is determined by \_\_\_\_\_ and \_\_\_\_

- State variable, current state

- Current state, flip-flop output

- Current state and external input

- Input and clock signal applied

10. A 8-bit serial in / parallel out shift register contains the value "8", \_\_\_\_\_ clock signal(s) will be required to shift the value completely out of the register.

5121

- ▶ 1

- ▶ 2

- ▶ 4▶ 8

11. The 4-bit 2's complement representation of "+5" is \_\_\_\_\_

- ▶ 1010

- ▶ 1110

- ▶ 1011

- > 0101

- 12. Stack is an acronym for \_\_\_\_\_

- FIFO memory

- LIFO memory

- Flash Memory

- Bust Flash Memory

#### 13. FIFO is an acronym for \_\_\_\_\_

- First In, First Out

- ➢ Fly in, Fly Out

- Fast in, Fast Out

- None of given options

#### 14. DRAM stands for \_\_\_\_\_

### Dynamic RAM

- Data RAM

- Demoduler RAM

- None of given options

#### 15. The alternate solution for a DE multiplexer-register combination circuit is \_

- Parallel in / Serial out shift register

- Serial in / Parallel out shift register

- > Parallel in / Parallel out shift register

- Serial in / Serial Out shift register

#### 16. In a state diagram, the transition from a current state to the next state is determined by

## Current state and the inputs

- Current state and outputs

- Previous state and inputs

- Previous state and outputs

## 17. \_\_\_\_\_ Counters as the name indicates are not triggered simultaneously.

- Asynchronous

- Synchronous

- Positive-Edge triggered

- Negative-Edge triggered

## 18. "A + B = B + A" is

- DE Morgan's Law

- Distributive Law

- Commutative Law

- Associative Law

- 19. For a positive edge-triggered J-K flip-flop with both J and K HIGH, the outputs will \_\_\_\_\_ if the clock goes HIGH.

- ➤ Toggle

- > Set

- Reset

- Not change

## Subjective

## **5** Questions Each have 3 Marks.

Q # 41:

Two state assignments are given in the table below. Identify which state assignment is best and why?

States

State assignment 1

A

00

| States | State assignment 1 | State assignment 2 |

|--------|--------------------|--------------------|

| Α      | 00                 | 00                 |

| В      | 01                 | 01                 |

| С      | 11                 | 10                 |

| D      | 10                 | 11                 |

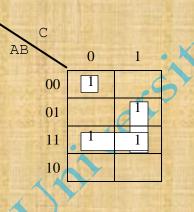

Determine the SOP Expression for Karnaugh map given below

### Q # 43:

Draw the Symbol of Operational Amplifier (Op-Amp). Q # 44:

Write the Difference b/w Counter and Shift register? Q # 55:

What are the modes in which a D-Latch Operations?

# **5** Questions Each have 5 marks:

Q # 46:

Give Function Table of 8 Input Multiplexer using two 4 Input Multiplexer. O # 47:

Two Input Combination for which the gated S-R Latch maintain its previous state? O # 48:

This is State diagram of a Mealy Machine. Draw the Next State Table of Mealy Machine and showing Present State, Next State, Input and Output.

Q # 49:

Write The Test Vector Definition of 3-bit Up/Down Counter. Q # 50: Write the answer as Yes or No in Column C.

| Column A | Column B                | Column C                 |

|----------|-------------------------|--------------------------|

| SRAM     | One-Transistor Cell     |                          |

| EEPROM   | High Density            | t contained an alter the |

| ROM      | In-System Write ability |                          |

| DRAM     | Non-Volatile            |                          |